# High Efficiency, Synchronous Buck with Dual Linear Controllers

### **General Description**

The RT9206 is a low cost, combo power controller, which integrates a synchronous step-down voltage-mode PWM and two HV linear controllers. Directly drive external N-MOSFET makes it easy to implement a high efficiency and cost attractive power solution. Voltage mode control loop and constant operation frequency with external compensation network provide better stability in wide operation range. Adjustable operation frequency up to 600kHz can minimize the inductor size and PCB space. It is particularly suitable in wide input voltage range (from 4.75V to 28V) and multi-output applications.

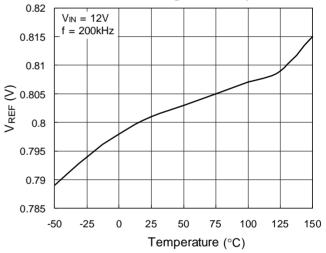

Linear controller features flexible linear power design. Delivered power can be simply decided by external N-MOSFET selection. Output voltage level is chosen via external resistor divider. The 0.8V internal reference can satisfy most of the applications. Under voltage lockout provide cost effective protection of output.

RT9206 provides complete safety protection function: soft start, over current protection, over voltage and under voltage protection. Set current limit by choosing different MOSFET. Synchronous Buck control mode provides excellent over voltage protection by turning on low side MOSFET to prevent any damage of end device from abnormal voltage stress as over voltage condition occurs.

### **Ordering Information**

RT9206 🖵 📮

Package Type S : SOP-16

- Operating Temperature Range

- P: Pb Free with Commercial Standard

- G : Green (Halogen Free with Commercial Standard)

#### Note :

RichTek Pb-free and Green products are :

- }RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- }Suitable for use in SnPb or Pb-free soldering processes.

- }100%matte tin (Sn) plating.

DS9206-11 March 2007

### Features

- Wide Input Range (4.75V to 28V)

- 0.8V Internal Reference

- High Efficiency Synchronous Buck Topology

- Integrate two HV Linear Controllers

- Low cost N-MOSFET Design

- Duty Cycle from 0% to 90%.

- Adjustable switching frequency from 200kHz to 600kHz, Default 200kHz

- Sense OCP by low Side MOSFET RDS(ON)

- Power Good Signal Output

- RoHS Compliant and 100% Lead (Pb)-Free

### Applications

- LCD Monitor

- ı Desk Note

- IEEE1394 Client

- ı Desktop IA

- I Broadband

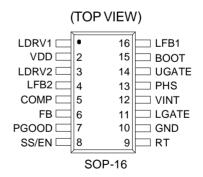

### **Pin Configurations**

1

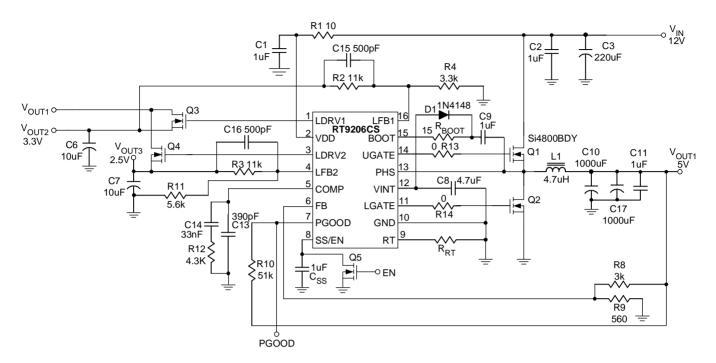

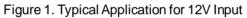

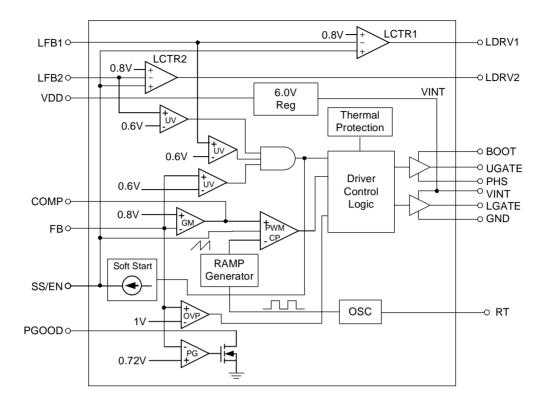

### **Typical Application Circuit**

Note : RBOOT is a must to suppress ringing spike.

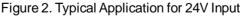

### **Function Block Diagram**

### Operation

### Introduction

The RT9206 is a combo controller, which integrates an adjustable frequency, voltage mode synchronous step down controller and two HV linear controllers. The synchronous step down controller consists of an internal precision reference, an internal oscillator, an error amplifier, a PWM comparator, control logic and floating gate driver, a programmable soft-start, a power good indicator, an over voltage protection, an over temperature protection and short circuit protection.

The output voltage of the synchronous converter is set and controlled by the output of the error amplifier, which is the amplified error signal from the sensed output voltage and the voltage on non-inverting input, which is connected with internal 0.8V reference voltage. The amplified error signal is compared to a fixed frequency linear sawtooth ramp and generates fixed frequency pulse of variable dutycycle, which drivers the two N-Channel external MOSFETs.

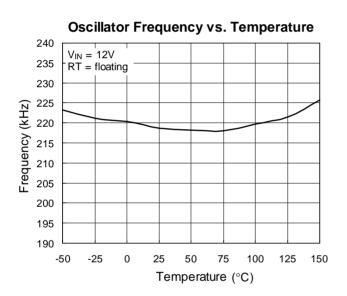

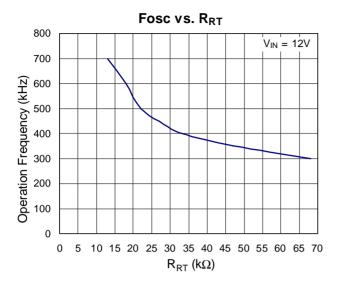

The timing of the synchronous converter is provide through an internal oscillator circuit and can be programmed between 200kHz to 600kHz via an external resistor connected between RT pin and ground.

#### Soft-Start

RT9206 has a programmable soft-start to control the output voltage rise time and limit the current surge at the startup. The soft-start will begin while V<sub>DD</sub> rises above POR threshold for correct start-up. Soft-start function operates by an internal sourcing current to charge an external capacitor to around the voltage of VINT. The soft-start signal, SS pin, is the third input non-inverting input of the PWM comparator. Before soft-start signal reach the bottom of the sawtooth ramp, inverting input of the PWM comparator, the soft-start current is twice of the normal soft-start current. Once the soft-start signal reach the bottom of the ramp, the soft-start current became normal, and start to increase duty cycle from zero to the point the feedback loop takes control.

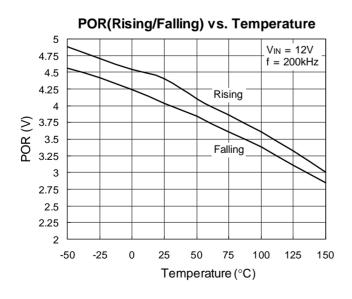

#### Power On Reset (POR)

The power on reset circuit assures that the MOSFET driver outputs remain in the off state whenever the  $V_{DD}$  supply voltages lower than the POR threshold.

### **Over-Current Protection**

Whenever the over-current is occurred in soft-start or in normal operation period, It will shut down PWM signal, the MOSFET driver outputs remain in the off state, and latch soft-start signal low until restart  $V_{DD}$  supply voltage.

### **Over-Voltage Protection**

Once over-voltage protection occurred, it will turn on low side MOSFET and latch soft-start signal low to prevent end device form abnormal voltage stress. Restart  $V_{DD}$  supply voltage will release the protection.

### **Power Good Indicator**

The power good indicator is an open drain output to show whether the synchronous converter output ready or not. The power good indicator is available after soft-start end.

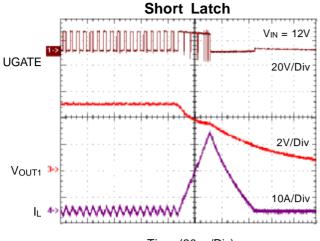

#### **Short-Circuit Protection**

The short-circuit phenomenon is sensed by the drop of output voltage, synchronous converter and two linear controller. Once the short-circuit occurred, the drop of output voltage lower than the under voltage threshold, 0.6V on feedback, the PWM signal will shut down and both of the external MOSFET will turn off and soft-start signal latch low. Soft-start signal, SS, is also connected to two linear controller error amplifier non-inverting input. Therefore, whenever the drop of output of the synchronous converter or two linear controllers lower than under voltage threshold, all MOSFET drivers will turn off.

### **Pin Description**

### LDRV1(Pin 1)

Linear controller 1 (LCTR1) driver. Connect to the gate of external N-Channel MOSFET pass transistor to form a positive linear regulator

### VDD (Pin 2)

Input supply voltage

### LDRV2 (Pin 3)

Linear controller 2 (LCTR2) driver. Connect to the gate of external N-Channel MOSFET pass transistor to form a positive linear regulator

### LFB2 (Pin 4)

LDO2 feedback input. The feedback set point is 0.8V. Connect to a resistive divider between the positive linear regulator output and GND to adjust the output voltage.

### COMP (Pin 5)

Switching regulator compensation pin.

### FB (Pin 6)

Switching regulator feedback input. The feedback set point is 0.8V. Connect to a resistive divider between the switching regulator output and GND to adjust the output voltage.

### PGOOD (Pin 7)

Open drain power good indicator. PGOOD is low when switching regulator output voltage is lower than 10% of its regulation voltage. Connect a pull high resistor between PGOOD and switching regulator output for pull high logic level voltage.

### SS/EN (Pin 8)

Soft start input with 8uA sourcing current and IC enable control.

### RT (Pin 9)

Operational frequency setting. Connect a resistor between RT and GND to set operational frequency. The operational frequency will nominally run at 200kHz when open.

The formula between resistor setting and operational frequency are as follows:

$$RRT = \frac{62 \times 10^8}{F_{OSC} - 200 \times 10^3}$$

### GND (Pin 10)

Ground

### LGATE (Pin 11)

Low side gate driver. Drives low side N-MOSFET with a voltage swing between VINT and GND

### VINT (Pin 12)

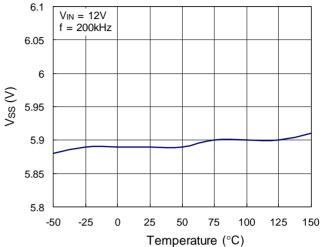

Internal 6.0V regulator output. The low side gate driver and control circuit and external bootstrap diode are powered by this voltage. Decouple this pin to power ground with a 4.7uF or greater ceramic capacitor close to the VINT pin.

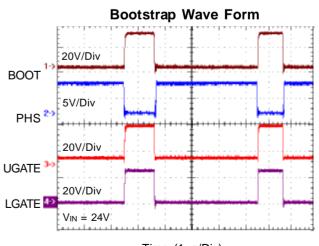

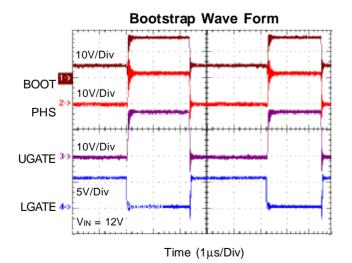

### PHS (Pin 13)

Inductor connection with (-) terminal bootstrap flying capacitor connection.

### UGATE (Pin 14)

High side gate driver. Drives high side N-Channel MOSFET with a voltage swing between BOOT and PHS

### BOOT (Pin 15)

High side floating driver supply with (+) terminal bootstrap flying capacitor connection. Voltage swing is from a diode drop below VINT to VIN+VINT

### LFB1 (Pin 16)

LDO1 feedback input. The feed back set point is 0.8V. Connect to a resistive divider between the positive linear regulator output and GND to adjust the output voltage.

### Absolute Maximum Ratings (Note 1)

| ı Supply Voltage (V <sub>IN</sub> )             | –0.3 to 30V  |

|-------------------------------------------------|--------------|

| ı PHS                                           |              |

| PHS (PHS Transient Time Interval < 50ns)        |              |

| I BOOT, UG to PHS                               |              |

| I BOOT to GND                                   |              |

| ı LDRI1, LDRI2                                  | 0.3V to 30V  |

| ۱ Power Good Voltage                            |              |

| 1 The other pins                                |              |

| Power Dissipation, $P_D @ T_A = 25^{\circ}C$    |              |

| SOP-16                                          | 0.625W       |

| Package Thermal Resistance                      |              |

| SOP-16, θ <sub>JA</sub>                         | 90°C/W       |

| ı Junction Temperature                          | 150°C        |

| Lead Temperature (Soldering, 10 sec.)           |              |

| Operation Temperature Range                     | 20°C to 85°C |

| I Storage Temperature Range                     |              |

| <ul> <li>ESD Susceptibility (Note 2)</li> </ul> |              |

| HBM (Human Body Mode)                           | 2kV          |

| MM (Machine Mode)                               | 200V         |

### Recommended Operating Conditions (Note 3)

| Ambient Temperature Range    | 0°C to 70°C  |

|------------------------------|--------------|

| ı Junction Temperature Range | 0°C to 125°C |

### **Electrical Characteristics**

$(V_{IN} = 12V, F_{ADJ}$  left floating,  $T_A = 25^{\circ}C$ , Unless Otherwise specification)

| Parameter                  | Symbol          | Test Condition                                          | Min  | Тур              | Max | Units |  |

|----------------------------|-----------------|---------------------------------------------------------|------|------------------|-----|-------|--|

| System Supply Input        |                 |                                                         |      |                  |     |       |  |

| Operation voltage Range    | V <sub>DD</sub> | (Note 4)                                                | 4.75 |                  | 28  | V     |  |

| Power On Reset             | POR             |                                                         | 3.8  |                  | 4.7 | V     |  |

| Power On Reset Hysteresis  |                 |                                                         | 200  |                  | 600 | mV    |  |

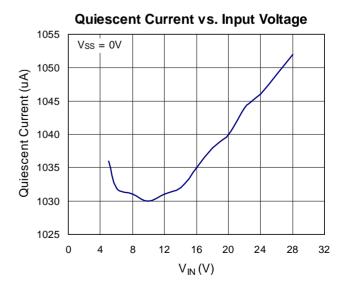

| Supply Current             | I <sub>DD</sub> | V <sub>DD</sub> =30V, V <sub>SS</sub> =V <sub>INT</sub> |      | 1.3              | 4   | mA    |  |

| Shut Down Current          | I <sub>DD</sub> | V <sub>DD</sub> =30V, V <sub>SS</sub> <0.4V             |      | 1                | 3.5 | mA    |  |

| Power Good under Threshold | VFB             |                                                         | 82   |                  | 92  | %     |  |

| PG Fault Condition         | VPG             | I <sub>PG</sub> = –4mA, VFB = 80%                       |      |                  | 0.2 | V     |  |

| Soft Start                 |                 |                                                         |      |                  |     |       |  |

| Soft start Current         | I <sub>SS</sub> |                                                         | 4    | 8                | 12  | μA    |  |

| Normal Operation Voltage   | V <sub>SS</sub> |                                                         |      | V <sub>INT</sub> |     | V     |  |

| Shut down Voltage          | V <sub>SS</sub> |                                                         | 0.4  | 0.7              |     | V     |  |

To be continued

| R' | Г9 | 2 | 0 | 6 |

|----|----|---|---|---|

| R  | Г9 | 2 | 0 | 6 |

| Parameter                                    | Symbol               | Test Condition                 | Min   | Тур  | Max   | Units    |

|----------------------------------------------|----------------------|--------------------------------|-------|------|-------|----------|

| PWM Section Reference Voltage                |                      |                                |       | I    |       | 1        |

| Feedback Voltage                             | V <sub>FB</sub>      |                                | 0.784 | 0.8  | 0.816 | V        |

| Internal Voltage                             | VINT                 | I <sub>INT</sub> = 10mA        | 5.0   | 6    | 6.5   | V        |

| Internal Voltage Source Current              | I <sub>INT</sub>     | V <sub>IN</sub> = 12V          | 20    |      |       | mA       |

| PWM Section<br>Oscillator                    |                      |                                |       |      |       |          |

| Free Run Frequency                           | Fosc                 |                                | 160   | 200  | 240   | kHz      |

| Operation Frequency Setting                  | Fosc                 | By setting RT (Note 5)         | -30   |      | +30   | %        |

| Ramp Amplitude                               |                      |                                |       | 1.9  |       | V        |

| Maximum Duty Cycle                           |                      |                                | 85    | 90   |       | %        |

| Error Amplifier                              |                      |                                |       |      |       |          |

| GM                                           |                      |                                |       | 1.6  |       | ms       |

| Compensation Source Current                  |                      |                                | 45    | 90   | 140   | μA       |

| Compensation Sink Current                    |                      |                                | 45    | 90   | 140   | μA       |

| Gate Driver                                  |                      |                                |       |      |       | <u>.</u> |

| Upper Gate Source (UGATE1 & 2)               | R <sub>UGATE</sub>   |                                |       | 5    | 8     | Ω        |

| Upper Gate Sink (UGATE1 & 2)                 | R <sub>UGATE</sub>   |                                |       | 5    | 8     | Ω        |

| Lower Gate Source (LGATE1 & 2)               | R <sub>LGATE</sub>   |                                |       | 3    | 5     | Ω        |

| Lower Gate Sink (LGATE1 & 2)                 | R <sub>LGATE</sub>   |                                |       | 1.5  | 3     | Ω        |

| Upper Gate Rising Time                       | T <sub>R_UGATE</sub> | $V_{DD} = 12V, C_{LOAD} = 3nF$ |       | 30   |       | ns       |

| Upper Gate Falling Time                      | T <sub>F_UGATE</sub> | $V_{DD} = 12V, C_{LOAD} = 3nF$ |       | 30   |       | ns       |

| Lower Gate Rising Time                       | T <sub>R_LGATE</sub> | $V_{DD} = 12V, C_{LOAD} = 3nF$ |       | 30   |       | ns       |

| Lower Gate Falling Time                      | T <sub>F_LGATE</sub> | $V_{DD} = 12V, C_{LOAD} = 3nF$ |       | 30   |       | ns       |

| Minimum On Time                              |                      |                                |       |      | 400   | ns       |

| Protection                                   |                      |                                |       |      |       |          |

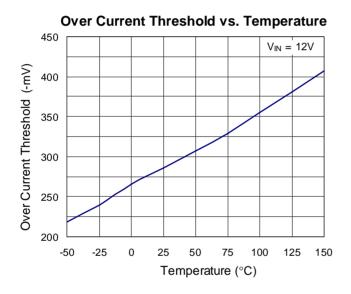

| Over Current Threshold                       |                      |                                | -270  | -300 | -330  | mV       |

| Over Voltage Protection                      | VFB                  |                                | 0.9   | 1    | 1.1   | V        |

| Under Voltage Protection                     | VFB                  |                                | 0.54  | 0.6  | 0.66  | V        |

| Linear Controller Section<br>Error Amplifier | ·                    |                                |       |      |       |          |

| Feedback Voltage                             | LFB1 / LFB2          |                                | 0.780 | 0.8  | 0.824 | V        |

| Output Current                               | LDRV1/LDRV2          |                                | 10    |      |       | mA       |

| Protection                                   |                      |                                |       |      |       |          |

| Under Voltage Protection                     | LFB1 / LFB2          |                                | 0.54  | 0.6  | 0.66  | V        |

| Over Temperature Protection                  |                      |                                | 125   | 170  |       | °C       |

- Note 1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- **Note 2.** Devices are ESD sensitive. Handling precaution recommended. The human body model is a 100pF capacitor discharged through a 1.5kΩ resistor into each pin.

- Note 3. The device is not guaranteed to function outside its operating conditions.

- Note 4. V<sub>DD</sub>-V<sub>OUT2</sub> or V<sub>DD</sub>-V<sub>OUT3</sub> must be higher than 4V to keep linear controller operation

Note 5.

$$R_{RT} = \frac{62 \times 10^8}{F_{OSC} - 200 \times 10^3}$$

**Note 6.** The LDOs are not suitable for low noise applications

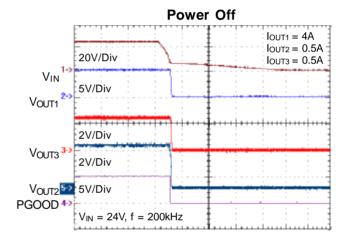

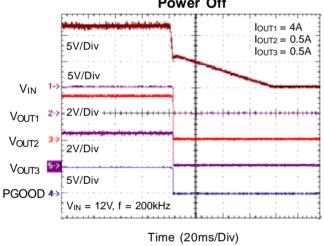

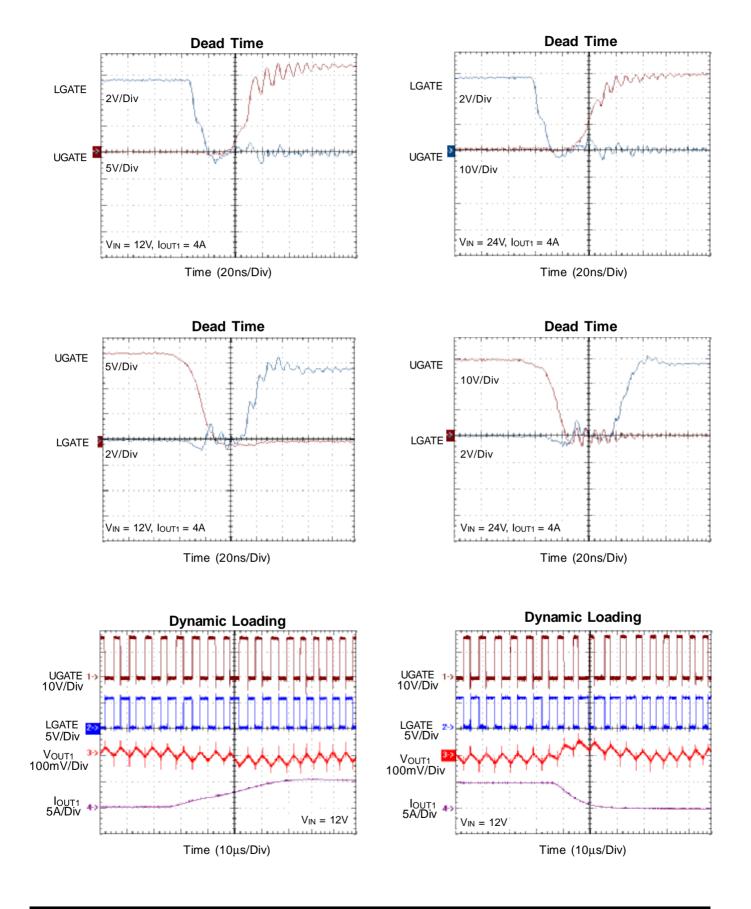

### **Typical Operating Characteristics**

Time (1µs/Div)

DS9206-11 March 2007

RICHTEK

www.richtek.com 10

Time (20µs/Div)

DS9206-11 March 2007

Soft Start vs. Temperature

**Reference Voltage vs. Temperature**

www.richtek.com

11

### **Application Information**

### Synchronous Buck Converter

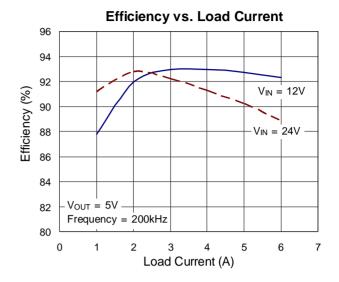

The RT9206 is specifically designed for synchronous buck converter with wide input voltage from 4.75V to 28V and operating frequency from 200kHz to 600kHz. To fully utilize its advantages, peripheral components should be appropriately selected. The following information provides basic considerations for component selection.

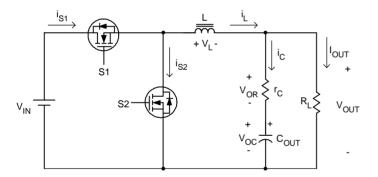

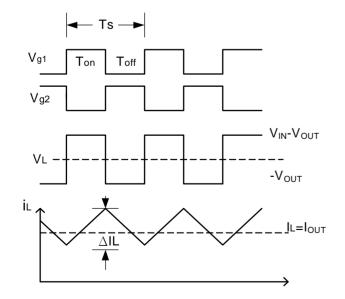

### **Output Inductor Selection**

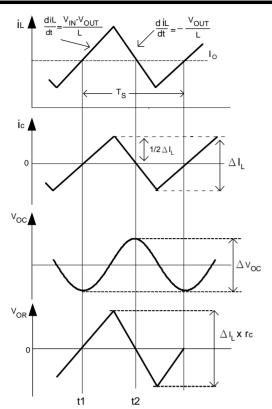

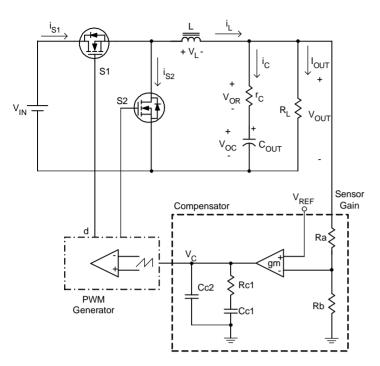

The selection of output inductor is based on the considerations of efficiency, output power and operating frequency. Low inductance value has smaller size, but results in low efficiency, large ripple current and high output ripple voltage. Generally, an inductor that limits the ripple current ( $\Delta I_L$ ) between 20% and 50% of output current is appropriate. Figure 1 shows the typical topology of synchronous step-down converter and its related waveforms.

Figure 1. The waveforms of synchronous step-down converter

According to Figure 1 the ripple current of inductor can be calculated as follows :

$$V_{IN} - V_{OUT} = L \frac{\Delta I_L}{\Delta t}; \Delta t = \frac{D}{fs}; D = \frac{V_{OUT}}{V_{IN}}$$

$$L = (V_{IN} - V_{OUT}) \times \frac{V_{OUT}}{V_{IN} \times fs \times \Delta I_L}$$

(1)

Where:

$V_{IN}$ = Maximum input voltage  $V_{OUT}$ = Output Voltage  $\Delta t=S_1$  turn on time  $\Delta I_L$ =Inductor current ripple  $f_S$ = Switching frequency D=Duty Cycle  $r_C$ = Equivalent series resistor of output capacitor

#### **Output Capacitor Selection**

The selection of output capacitor depends on the output ripple voltage requirement. Practically, the output ripple voltage is a function of both capacitance value and the equivalent series resistance (ESR)  $r_c$ . Figure 2 shows the related waveforms of output capacitor.

DS9206-11 March 2007

Figure 2. The related waveforms of output capacitor.

The AC impedance of output capacitor at operating frequency is quite smaller than the load impedance, so the ripple current ( $\Delta I_L$ ) of the inductor current flows mainly through output capacitor. The output ripple voltage is described as :

$$\Delta V_{OUT} = \Delta V_{OR} + \Delta V_{OC}$$

(2)

$$\Delta \text{Vout} = \Delta \text{IL} \times \text{rc} + \frac{1}{\text{Co}} \int_{\text{t1}}^{\text{t2}} \text{ic } dt$$

(3)

$$\Delta V_{OUT} = \Delta I_L \times rc + \frac{1}{8} \frac{V_{OUT}}{C_OL} (1 - D) T_s^2$$

(4)

where  $\Delta V_{OR}$  is caused by ESR and  $\Delta V_{OC}$  by capacitance. For electrolytic capacitor application, typically 90~95% of the output voltage ripple is contributed by the ESR of output capacitor. So Equation (4) could be simplified as :

$$\Delta V_{OUT} = \Delta I_L \times r_C$$

(5)

Users could connect capacitors in parallel to get calculated ESR.

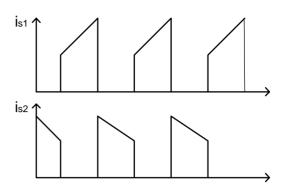

#### Input Capacitor Selection

The selection of input capacitor is mainly based on its maximum ripple current capability. The buck converter draws pulsewise current from the input capacitor during the on time of S1 as shown in Figure 1. The RMS value of ripple current flowing through the input capacitor is described as :

$$rms = IO\sqrt{D(1-D)}$$

(A) (6)

The input capacitor must be cable of handling this ripple current. Sometime, for higher efficiency the low ESR capacitor is necessarily.

#### **Power MOSFET Selection**

The selection of MOSFETs is based on consideration of maximum gate-source voltage (Vgs), drain-source voltage (Vdss), maximum drain current (Id), drain-source on-state resistance  $R_{ds(on)}$  and thermal management. The MOSFETs are driven by  $V_{INT}$  that is internally regulated as 6.0V. Low threshold voltage MOSFET should be selected to guarantee that it could fully turn on at Vgs = 6.0V.

The total power dissipation of external MOSFETs consists of conduction and switching losses. The conduction losses of high-side and low-side MOSFETs are described by equation (7) and (8), respectively.

#### (High-side MOSFET)

$$PH - con = I_0^2 \times D \times Rds(on) \times qr \qquad (W)$$

(7)

(Low-side MOSFET)

$$PL - con = I_0^2 \times (1 - D) \times Rds(on) \times qr$$

(W) (8)

Where

qr is temperature dependency of  $\mathsf{R}_{\mathsf{ds(on)}}$

The total switching loss is approximated as.

$$\mathsf{Psw} = \mathsf{I}_{\mathsf{OUT}} \times \frac{\mathsf{Vds}(\mathsf{off})}{2} \times (\mathsf{tr} + \mathsf{tf}) \times \mathsf{fs} \ (\mathsf{W}) \tag{9}$$

Where

$V_{\text{ds(off)}}$  is voltage from drain to source at MOSFET off time.

$t_r$  and  $t_f$  are rise-time and fall-time, respectively.

IOUT= Load current

fs= Switching frequency

The MOSFET should be capable of handling the power loss over the entire operating range.

### **Design Example:**

Design the power stage for a synchronous step-down converter having the following specifications:

$V_{IN}$ = 12V,  $V_{OUT}$  = 5V,  $I_{OUT}$  = 5A,  $\Delta V_{OUT}$  < 25mV, switching frequency = 200kHz, to determine the value of inductor and output capacitor (Using electrolytic capacitor).

First, select ripple current of inductor is 20% of output current, from equation (1)

$$L = (12 - 5) \times \frac{5}{12 \times 200 \text{K} \times 0.2 \times 5} = 14.58 \text{ mH}$$

Select L =  $15\mu$ H

From equation (5)

Select two electrolytic capacitors C =  $470\mu$ F,r<sub>C</sub> =  $43m\Omega$  in parallel.

### **Setting the Current Limit**

The RT9206 limits output current by sensing low side MOSFET voltage drop ( $V_{SD}$ ) when it turns on. The drop voltage caused by on-state resistance  $R_{DS(ON)}$  is described as :

$$V_{SD} = R_{DS(ON)} \times I_L$$

(10)

When V<sub>SD</sub> >300mV, the current limit function will be activated and latch the controller. So the current limit function can be set by MOSFETs selection. The relation of maximum inductor current  $I_{L(LIM)}$  and on-state resistance of MOSFET (R<sub>DS(ON)</sub>) is described as :

$$R_{DS(ON)} = \frac{300 \times 10^{-3}}{I_{L(LIM)}} \qquad (\Omega) \qquad (11)$$

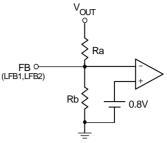

#### Setting the Output voltage

The output voltage is set by external voltage divider and reference voltage. The feedback pin (FB, LFB1, and LFB2) is connected to the inverting input of error amplifier and is referenced to 0.8V reference voltage at non-inverting input as shown in Figure 3.The output voltage is set by the following equation.

$$V_{OUT} = (1 + \frac{Ra}{Rb}) \times 0.8$$

(12)

DS9206-11 March 2007

Figure 3. The connected diagram of external voltage divider and reference voltage

If high value resistors are used, the input bias current of FB pin could cause a slight increase in output voltage. The output voltage set point can be more accurate by using precision resistor.

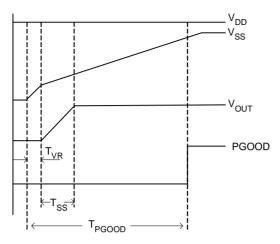

#### Soft-start setting

Figure 4 shows the typical soft-start timing waveforms of RT9206. The soft-start time of Buck converter can be set by selecting the soft-start capacitance value. The delay time between input voltage applied and output voltage starting to ramp up ( $T_{DELAY}$ ) is calculated as: The total time from input voltage applied to output voltage buildup ( $T_{VR}$ ) is calculated as :

$$T_{VR} = 57 \times C_{SS} \times 10^6$$

(ms) (13)

The effective soft-start time ( $T_{SS}$ ) during that output voltage ramps up from zero to set voltage is calculated as :

$$Tss = (320 \times \frac{Vout}{V_{IN}}) \times 10^6 \times Css \qquad (ms) \quad (14)$$

Besides, appropriate soft-start capacitor should be selected so that the start-up current will not trigger the current limit function. And make sure that the input power source could supply the soft-start current.

The total time from input voltage applied to power good signal pull-high ( $T_{PGOOD}$ ) is calculated as :

$$T_{PG} = 640 \times C_{SS} \times 10^6$$

(ms) (15)

Figure 4. The soft-stat timing diagram of RT9206

For the example of  $C_{SS} = 1\mu F$ ,  $V_{IN} = 12V$ ,  $V_{OUT} = 5V$ , then  $T_{VR} = 57ms$ ,  $T_{SS} = 133ms$  and  $T_{PGOOD} = 640ms$ .

### Shutdown

The power stage can be shutdown by pulling soft-start pin below 0.7V. During shutdown, both of high side MOSFET (S1) and low side MOSFET (S2) are turned off.

### Setting the switching frequency

The switching frequency can be set by a resistor ( $R_{RT}$ ) connecting between RT and GND pins. Equation (16) describes the relationship of  $R_{RT}$  and switching frequency. As  $R_T$  open the normally operated frequency is 200kHz.

$$R_{RT} = \frac{62 \times 10^8}{\text{fs} - 200 \times 10^3} \qquad (\Omega) \qquad (16)$$

| R <sub>RT</sub> Connecting Between        |      |  |  |  |

|-------------------------------------------|------|--|--|--|

| RT and GND Pins                           |      |  |  |  |

| f <sub>S</sub> (kHz) R <sub>RT</sub> (kΩ) |      |  |  |  |

| 250                                       | 120  |  |  |  |

| 300                                       | 55   |  |  |  |

| 350                                       | 37.5 |  |  |  |

| 400                                       | 30.6 |  |  |  |

| 450                                       | 24.4 |  |  |  |

| 500                                       | 22.5 |  |  |  |

| 550                                       | 19.3 |  |  |  |

| 600                                       | 16.8 |  |  |  |

### **Boost Component Selection**

The booststrap gate drive circuit is used to drive high side N-channel MOSFET. The boost capacitor should be a good quality and can operate in high frequency. The value of boost capacitor depends on the total gate charge ( $Q_Hg$ ) to turn on the MOSFETs. Assuming steady state operation, the following equation can be used to calculate the capacitance value to achieve the targeted ripple voltage  $DV_{BOOT}$ .

$$C_{BOOT} = \frac{Q_{Hg}}{\Delta V_{BOOT}}$$

(F)

The capacitor in the range of 0.1uF to 1uF is generally adequate for most applications.

The VINT pin bypass capacitor  $C_{INT}$  needs to charge the boost capacitor, to drive the low side MOSFET, and to power the RT9206.  $C_{INT}$  should locate near VINT and GND pins with short and wide traces. Generally, a 4.7uF high frequency ceramic capacitor is recommended.

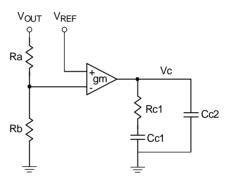

### Feedback Compensation

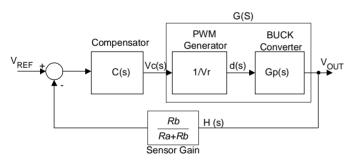

The RT9206 is a voltage mode controller. The control loop is a single voltage feedback loop including a transconductance error amplifier and a PWM comparator.

To achieve fast transient response and accurate output regulation, appropriate feedback compensation is necessary. The goal of the compensation network is to provide a closed loop transfer function with the highest 0dB crossing frequency and adequate phase margin. Generally, the phase margin in a range of  $45^{\circ} \sim 60^{\circ}$  is desirable. Figure 4 shows the simplified diagram of synchronous buck converter and control loop.

Figure 5. The simplified diagram for synchronous Buck converter and control loop.

From control system point of view, the block diagram of Figure 5 is shown in Figure 6.

Figure 6. The control block diagram of synchronous Buck converter

First, deriving the accurate small-signal models of power stage, the equation (18) is the transfer function of  $v_0(s)/d(s)$ , which be obtained by space averaging technique.

$$G_{P(S)} = \frac{V_{OUT(S)}}{d(S)} = \frac{1 + rc \ x \ Co \ x \ S}{S^2 \ x \ L \ x \ Co} + S(\frac{L}{RL} + rc \ x \ Co) + 1} \ x \ V_{IN}$$

(18)

DS9206-11 March 2007

**RT9206**

Next, deriving the transfer function  $d(s)/v_C(s)$  of the direct duty ratio pulse-width modulator (PWM Generator). The transfer function  $T_m(s)$  of the modulator is given by

$$T_{m}(s) = \frac{d(s)}{V_{C}(s)} = \frac{1}{Vr}$$

(19)

where,  $V_r$  is the amplitude of ramp-waveform which is listed in datasheet.

For simplification, the transfer function of PWM generator and Buck converter can is combined. The resulting is shown in equation (20)

$$G(s) = \frac{V_{OUT(S)}}{V_{C(S)}} = \frac{1 + \text{rc } x \text{ Co } x \text{ S}}{S^2 x \text{ L} + \text{Co } x \text{ S}(\frac{L}{R_L} + \text{rc } x \text{ Co}) + 1} x \frac{V_{IN}}{Vr}$$

(20)

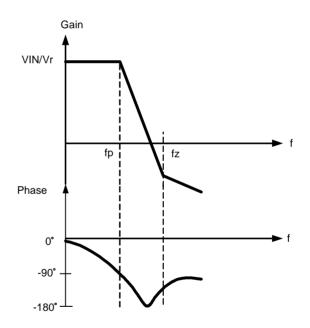

The transfer function of Equation (20) is a second order system and Bode plot is shown in Figure 7.

Figure 7. The Bode plot of Buck power stage

In Figure 7, the resonance of the output LC filter produces a double pole and -40dB/decade slop. The resonance frequency is expressed as follows :

$$f_{P} = \frac{1}{2p \times \sqrt{L \times Co}}$$

(Hz) (21)

The effective series resistance (ESR) of capacitor and capacitance introduces one zero into system, the zero is given as :

$$fz = \frac{1}{2p \, x \, rc \, x \, Co} \tag{Hz}$$

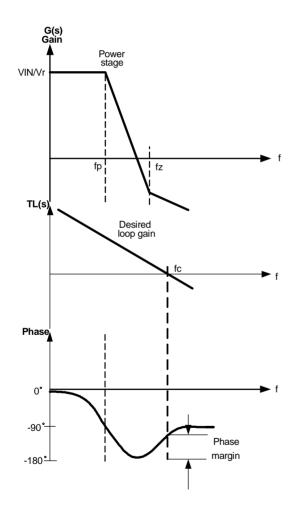

In the voltage-mode Buck converter shown in Figure 5, the loop gain of system is

$$T_{L(S)} = C(S) \times \frac{1}{Vr} \times G_{P(S)} \times H(S) = C(S) \times G(S) \times H(S)$$

(23)

The desired loop gain and phase margin is show in the Bode plot of Figure 8.

Where the  $f_C$  is zero crossover frequency defined as the frequency when the loop gain equals unity. Typically,  $f_C$  be chosen in range 1/10 ~ 1/20 of switching frequency.  $f_C$  determines how fast the dynamic load response is. The higher  $f_C$  with the faster dynamic response, and the phase margin in the range of  $45^\circ \sim 60^\circ$  is desirable.

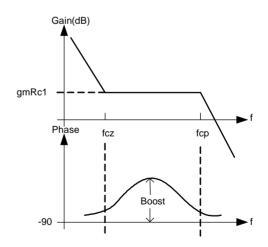

So, the transfer function of compensator C(s) must be designed to meet these requirements. In many applications, use an electrolytic capacitor as the output capacitor, if the zero ( $f_Z$ ) caused by effective series resistance (ESR) of capacitor is a few kHz and smaller than 8 times  $f_P$ , the type 2 (PI) can be used to get desired compensation. Figure 9 shows the typical type 2 trans-conductance error amplifier and the Bode plot is also shown in Figure 10.

Figure 9. The typical type 2 trans-conductance error amplifier.

Figure 10. The Bode plot of type 2 trans-conductance error amplifier

The design procedure as following :

(1). Selecting the zero crossover frequency  $f_C$  is  $1/10 \sim 1/20$  switching frequency. Then according equation (24) set the resistor  $R_{C1}$  to determine the zero crossover frequency.

$$Rc_{1} \approx \frac{Vr \times L \times fc}{V_{IN} \times gm \times rc} \times \frac{Vout}{V_{REF}} \quad (\Omega) \qquad (24)$$

(2). Place the zero of compensator is 70% fp that is resonance frequency of power stage. The compensator capacitor Cc1 can be selected to set the zero. The equation is shown in following :

$$C_{C1} = \frac{\sqrt{L \times C_0}}{0.7 \times R_{C1}}$$

(F) (25)

(3). Set a second pole to suppress the switching noise. Assume the pole is one half of switching frequency  $f_s$ , which results in capacitor Cc2 as shows in following:

$$C_{C2} = \frac{1}{p \times R_{C1} \times f_{S}} = \frac{1}{\frac{1}{C_{C1}}} \approx \frac{1}{p \times R_{C1} \times f_{S}} \quad (F) \quad (26)$$

#### Design example

Design example of type 2 compensator: the schematic is shown in Figure 4, where the parameters as following:  $V_{IN}=12V$ ,  $V_{OUT}=5V$ ,  $I_{OUT}=5A$ , switching frequency=200kHz, L=15 $\mu$ H, C<sub>0</sub>=940 $\mu$ F, r<sub>C</sub>=22m $\Omega$ , the parameters of RT9206 as following: gm=1.6ms, ramp amplitude=1.9V,and reference voltage Vref=0.8V.

Step1. Determine the power stage poles and zeros. The pole caused by the output inductor and output capacitor is calculated as :

$$f_{P} = \frac{1}{2p\sqrt{L \times Co}} = \frac{1}{2p\sqrt{15m \times 940m}} = 1.34 \text{ kHz}$$

$$f_{Z} = \frac{1}{2p \times \text{rc} \times \text{Co}} = \frac{1}{2p \times 22m\Omega \times 940m} = 7.7 \text{ kHz}$$

Step2. Determine the zero crossover frequency and compensated type.

Select desired zero-crossover frequency :

$$fc \le fs/10 \sim fs/20$$

Select

$$f_C = 20kHz$$

Step3. Determine desired location of poles and zeros for type2 compensator.

Select:

$$fcz = 0.7 \times fP = 0.7 \times 1.34 kHz = 938Hz$$

Assume

$$f_{CP} = \frac{f_S}{2} = 100 \text{ kHz}$$

Step4. Calculate the real parameters-resistor and capacitors for type2 compensator.

From equation (21), the R<sub>C1</sub> is calculated as following :

$$Rc_{1} = \frac{fc \times L \times Vr}{rc \times ViN \times gm} \times \frac{Vout}{VREF}$$

$$= \frac{20kHz \times 15mH \times 1.9}{22m\Omega \times 12V \times 1.6ms} \times \frac{5V}{0.8V} = 8.4k\Omega$$

Select  $R_{C1} = 8.2 k\Omega$

Calculate  $C_{C1}$  from equation (25)

$$Cc_{1} = \frac{\sqrt{L \times Co}}{0.7 \times Rc_{1}} = \frac{\sqrt{15m \times 940m}}{0.7 \times 8.2k} = 20.7 \text{nF}$$

Select C<sub>C1</sub> = 22nF

Second capacitor  $C_{C2}$  can be calculated using equation (26)

$$C_{C2} = \frac{1}{p \times R_{C1} \times f_{S}} = \frac{1}{p \times 8.2 k\Omega \times 200 kHz} = 194 pF$$

Select C<sub>C2</sub> = 220pF

### Linear Regulator

### **Output Capacitor Selection**

Solid tantalum capacitors are recommended for use on the output capacitors of LDO because their typical ESR is very close to the ideal value required for loop compensation. Tantalums also have good temperature stability: a good quality tantalum will typically show a capacitance value that varies less than 10-15% across the full temperature range of 125°C to -40°C. ESR will vary only about 2X going from the high to low temperature limits.

### Linear Regular MOSFETs Selection

The main consideration of pass MOSFETs of linear regulator is package selection for efficient removal of heat. The power dissipation of a linear regulator is

The criterion for selection of package is the junction temperature below the maximum desired temperature with the maximum expected ambient temperature.

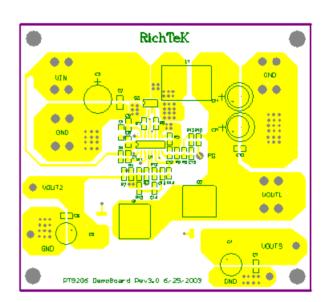

### Layout Consideration

Layout is very important in high frequency switching converter design. If designed improperly, the PCB could radiate excessive noise and contribute to the converter instability. First, place the PWM power stage components. Mount all the power components and connections in the top layer with wide copper areas. The MOSFETs of Buck, inductor, and output capacitor should be as close to each other as possible. This can reduce the radiation of EMI due to the high frequency current loop. If the output capacitors are placed in parallel to reduce the ESR of capacitor, equal sharing ripple current should be considered. Place the input capacitor directly to the drain of high-side MOSFET. The MOSFETs of linear regulator should have wide pad to dissipate the heat. In multilayer PCB, use one layer as power ground and have a separate control signal ground as the reference of the all signal. To avoid the signal ground is effect by noise and have best load regulation, it should be connected to the ground terminal of output. Furthermore, follows below guidelines can get better performance of IC:

- The IC needs a bypassing ceramic capacitor C1 as a R-C filter to isolate the pulse current from power stage and supply to IC, so the ceramic capacitor C1 should be placed adjacent to the IC.

- (2). Place the high frequency ceramic decoupling close to the power MOSFETs.

- (3). The feedback part should be placed as close to IC as possible and keep away from the inductor and all noise sources.

- (4). The components of bootstraps (C8, C9 and D1) should be closed to each other and close to MOSFETs.

- (5).The PCB trace from UGATE and LGATE of controller to MOSFETs should be as short as possible and can carry 1A peak current.

- (6). Place all of the components as close to IC as possible.

Buck converter with RT9206 controller

Figure 11 shows the typical PCB layout of synchronous

Figure 11. The PCB layout of synchronous Buck converter with RT9206 controller

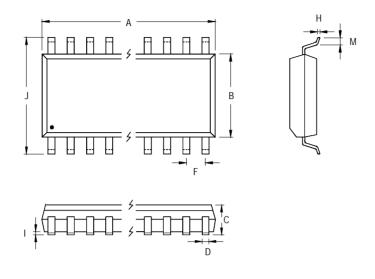

### **Outline Dimension**

| Symbol | Dimensions In Millimeters |        | Dimension | s In Inches |

|--------|---------------------------|--------|-----------|-------------|

| Symbol | Min                       | Max    | Min       | Max         |

| А      | 9.804                     | 10.008 | 0.386     | 0.394       |

| В      | 3.810                     | 3.988  | 0.150     | 0.157       |

| С      | 1.346                     | 1.753  | 0.053     | 0.069       |

| D      | 0.330                     | 0.508  | 0.013     | 0.020       |

| F      | 1.194                     | 1.346  | 0.047     | 0.053       |

| Н      | 0.178                     | 0.254  | 0.007     | 0.010       |

| I      | 0.102                     | 0.254  | 0.004     | 0.010       |

| J      | 5.791                     | 6.198  | 0.228     | 0.244       |

| М      | 0.406                     | 1.270  | 0.016     | 0.050       |

16-Lead SOP Plastic Package

### **Richtek Technology Corporation**

Headquarter 5F, No. 20, Taiyuen Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789 Fax: (8863)5526611

### **Richtek Technology Corporation**

Taipei Office (Marketing) 8F, No. 137, Lane 235, Paochiao Road, Hsintien City Taipei County, Taiwan, R.O.C. Tel: (8862)89191466 Fax: (8862)89191465 Email: marketing@richtek.com

DS9206-11 March 2007